# Hermetic and Non-Hermetic QML Space ICs -Status and Challenges CMSE 2017 Components for Military and Space Electronics

Los Angeles, California April 11–13, 2017

#### S. Agarwal

NASA - Jet Propulsion Laboratory, California Institute of Technology Pasadena, California, USA Shri.g.agarwal@jpl.nasa.gov

Curiosity Rover Finds and Examines a Meteorite on Mars The dark, smooth-surfaced rock at the center of this Oct. 30, 2016, image from the Mast Camera (Mastcam) on NASA's Curiosity Mars rover was examined with laser pulses and confirmed to be an iron-nickel meteorite.)

#### Contents

#### • Parts Standards - NASA's NEPAG Program

- What is NEPAG

- How we interact with the user community, manufacturers and others

- Process to resolve major issues

#### • QML Space ICs

- Hermetic (Class V)

- Ceramic based vented packages (Class Y)

#### Concluding Remarks

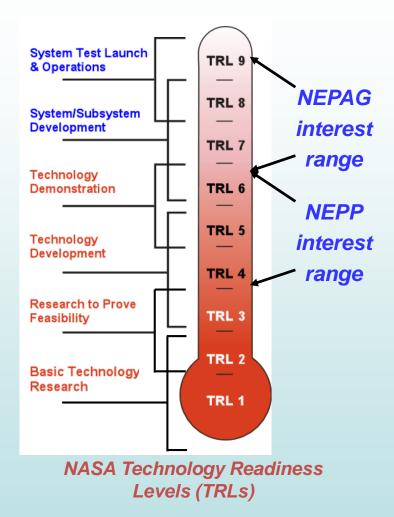

### **NEPP/NEPAG Focus**

- NEPP = NASA Electronic Parts and Packaging Program

- NEPAG = NASA Electronic Parts Assurance Group

- Funded by NASA Office of Safety and Mission Assurance (OSMA)

- Co-managed by Mike Sampson and Ken LaBel

- JPL funding comes through 5X Assurance Technology Program Office (ATPO) managed by Doug Sheldon

## **NEPAG Activities**

#### • Weekly Telecons

- A forum for effective exchange of information on electronic parts used on flight projects across NASA (OneNASA) and the space parts community (OneSpace). In its 17<sup>th</sup> year of operation, NEPAG is comprised of 25 organizations including 7 NASA centers, JPL and 3 international partners from Europe, Japan, and Canada (ESA, JAXA, CSA, respectively).

- These telecons drive the NEPAG program:

#### • Support to Defense Logistics Agency (DLA) – Audits, SMD Reviews

- The Defense Logistics Agency (DLA), the Aerospace Corporation and NASA form the space microcircuits qualifying activity (QA). Therefore, NASA is actively involved in the audits and standards activities.

- Audits: VQ is the audits branch of DLA. NASA supports about 25% of the audits DLA does. We lead audit teams in areas such as burn-in and electrical test program reviews.

- Standard Microcircuit Drawings (SMDs): VA is the standards/documentation branch of DLA. We review SMDs for new space products. The SMD program is going strong with about 18–20 new space SMDs created every year.

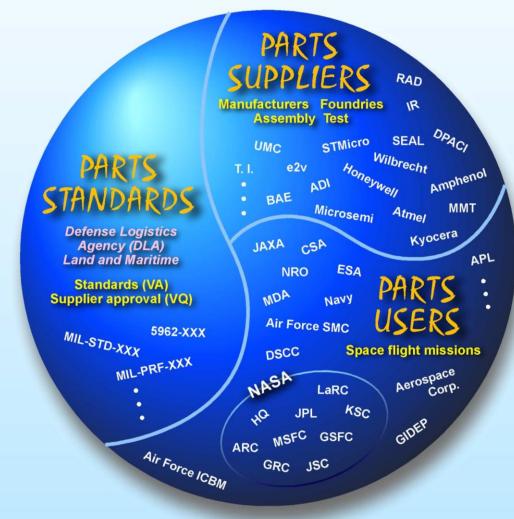

#### **Space Parts World** Develop/Maintain Standards for Space Electronic Parts

NEPAG

The parts users and standards organizations work with suppliers to ensure availability of standard parts for NASA, DoD and others. For Space microcircuits, DLA, NASA/JPL (S. Agarwal) and the U.S. Air Force / Aerospace Corp. (L. Harzstark) form the Qualifying Activity (QA).

### A Changing Landscape (Shipping/Handling/ESD Challenge)

A New Trend – Supply Chain Management Ensuring gap-free alignment for each qualified product (All entities in the supply chain must be certified/approved)

| Manufacturer A | Die design                               |

|----------------|------------------------------------------|

| Manufacturer B | Fabrication                              |

| Manufacturer C | Wafer bumping                            |

| Manufacturer D | Package design and package manufacturing |

| Manufacturer E | Assembly                                 |

| Manufacturer F | Column attach and solderability          |

| Manufacturer G | Screening, electrical and package tests  |

| Manufacturer H | Radiation testing                        |

### An Example of SMD Boiler-Plate Update

| TABLE IIA. | Electrical t | est req | uirements. |

|------------|--------------|---------|------------|

|            |              |         |            |

| Line<br>Number | Test requirements                                     | Subgroups (in accordance with<br>MIL-PRF-38535, table III) |                                        |  |  |

|----------------|-------------------------------------------------------|------------------------------------------------------------|----------------------------------------|--|--|

| Number         |                                                       | Device class Q                                             | Device class V                         |  |  |

| 1              | Interim electrical parameters (see 4.2)               | 1,2,3,7,8A,<br>8B,9,10,11 <u>1</u> /                       | 1,2,3,7,8A,<br>8B,9,10,11 <u>1</u> /   |  |  |

| 2              | Static burn-in I and II<br>(method 1015)              | Not required                                               | Required                               |  |  |

| 3              | Same as line 1                                        |                                                            | 1,7 Δ <u>1</u> / <u>2</u> /            |  |  |

| 4              | Dynamic burn-in<br>(method 1015)                      | Required                                                   | Required                               |  |  |

| 5              | Same as line 1                                        | 1,7 Δ <u>1</u> / <u>2</u> /                                | 1,7∆ <u>1</u> / <u>2</u> /             |  |  |

| 6              | Final electrical parameters                           | 1,2,3,7,8A,8B,9,<br>10,11 <u>1</u> /                       | 1,2,3,7,8A,8B,9,<br>10,11 <u>1</u> /   |  |  |

| 7              | Group A test requirements <u>3</u> /                  | 1,2,3,4,7,8A,8B,9,10<br>,11 <u>4</u> /                     | 1,2,3,4,7,8A,8B,9,<br>10,11 <u>4</u> / |  |  |

| 8              | Group C end-point electrical parameters <u>3</u> /    | 1,2,3,7,8A,8B,<br>9,10,11 ∆ <u>2</u> /                     | 1,2,3,7,8A,8B,<br>9,10,11 ∆ <u>2</u> / |  |  |

| 9              | Group D end-point electrical parameters <u>5</u> /    | 2,3,8A,8B                                                  | 2,3,8A,8B                              |  |  |

| 10             | Group E end-point electrical parameters<br><u>3</u> / | 1,7,9                                                      | 1,7,9                                  |  |  |

| 11             | Column attach <u>6</u> /                              | 1,7,9                                                      | 1,7,9                                  |  |  |

#### • For Flip-chip column attach

Add room temperature electricals (subgroups 1, 7, 9) after column attach – step 11 above

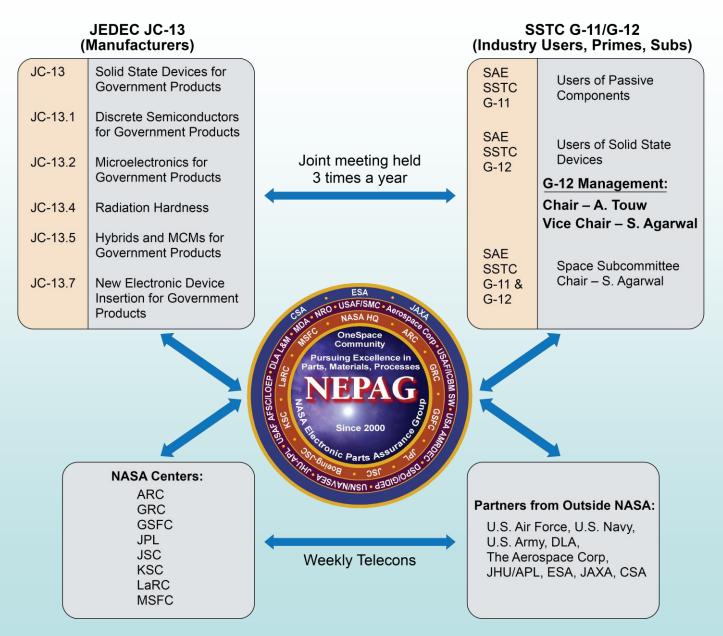

#### Partnering with Industry Groups, NASA Centers, Space Agencies

### JEDEC/G-11/G-12 Grid (January 2017)

| n Anton       | 110, 1 X                             |                           |                                                                    |                              |                                                                                                      |                                           |                                                              | INAL<br>g Schedule                         |                                                |                                            |                                         | NEPAG M                                     | TG.                                                      | January      |

|---------------|--------------------------------------|---------------------------|--------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------|--------------------------------------------|------------------------------------------------|--------------------------------------------|-----------------------------------------|---------------------------------------------|----------------------------------------------------------|--------------|

| Day           | Room                                 | 7:30 AM                   | 8:00 AM                                                            | 9:00 AM                      | 10:00 AM                                                                                             | 11:00 AM                                  | 12:00 PM                                                     | 1:00 PM                                    | 2:00 PM                                        | 3:00 PM                                    | 4:00 PM                                 | 5:00 PM                                     | 6 PM                                                     | 7PM          |

| Mon 1/9       | Regency East 1-3<br>(Ballroom Level) |                           |                                                                    |                              |                                                                                                      |                                           |                                                              | G-12 Derating/<br>Wear-out and<br>Profiles | G-12 Terrestrial &<br>Avionics<br>Subcommittee | G-12 PEM TG Qual and<br>Screening Flow     | G-12 Plastics /<br>PEMS<br>Subcommittee | ESD EP Study                                | **                                                       |              |

|               | Chula Vista<br>(Lobby Level)         |                           |                                                                    |                              |                                                                                                      |                                           | MIL-PRF-19500R JC-13.1 should attend PEMs Screening flow Rev |                                            |                                                |                                            |                                         |                                             |                                                          |              |

|               | Live Oak (Hill<br>Country Level)     | (                         |                                                                    |                              |                                                                                                      | (                                         | JC-13 ExCo Mtg.<br>(by invitation)                           | * JC-13.5 TG 175 - PI / QML Task Group     |                                                |                                            |                                         |                                             |                                                          |              |

| Day           |                                      | 7:30 AM                   | 8:00 AM                                                            | 9:00 AM                      | 10:00 AM                                                                                             | 11:00 AM                                  | 12:00 PM                                                     | 1:00 PM                                    | 2:00 PM                                        | 3:00 PM                                    | 4:00 PM                                 | 5:00 PM                                     | 6 PM                                                     | 7PM          |

|               | Regency East 1-3<br>(Ballroom Level) | New Member<br>Orientation | JC-13.1/JC-<br>13.7/G-12 New<br>Technology<br>Appendix in<br>19500 | JC-13.1 GaN<br>Working Group | JC-13.1/JC-13.7/G-<br>12 SIC Tech<br>Insertion                                                       | JC-13.7 >2D<br>Packaging                  |                                                              | JC-13/G-12 Joint<br>Meeting                | JC-13.7 Copper Wire<br>Bonds                   | JC-13.2<br>Elec Parameters & B/I<br>Stand. | JC-13<br>X-Ray Seal<br>Voids            | JC-13<br>Leak Rate Issues ir<br>883 and 750 | G-12 & G-11<br>Counterfeit<br>Mitigation<br>Subcommittee |              |

| ues 1/10      | Pecan (Hill<br>Country Level)        |                           |                                                                    |                              | JC-13.2 JEP121                                                                                       | JC-13.1 should<br>attend >2D<br>Packaging |                                                              |                                            |                                                | JC-13.1 MIL-PRF-19500<br>Appendix J        |                                         | JC-13.1 should attend leak rate             |                                                          |              |

|               | Chula Vista<br>(Lobby Level)         |                           |                                                                    | 3158 - Element<br>aluation   | MIL-STD-883<br>Inspection and<br>Interpretation                                                      | JC-13.5 TG 172<br>QML Reqs.               |                                                              | X                                          |                                                | TM2017 End<br>termination inspection       |                                         |                                             |                                                          |              |

|               | Live Oak (Hill<br>Country Level)     |                           | JC-13.4 Subcommittee Meeting                                       |                              |                                                                                                      | $/ \wedge$                                | $/ \setminus$                                                | JC-13.4 Extended<br>Session                |                                                |                                            |                                         |                                             |                                                          |              |

| Day           |                                      | 7:30 AM                   | 8:00 AM                                                            | 9:00 AM                      | 10:00 AM                                                                                             | 11:00 AM                                  | 12:00 PM                                                     | 1:00 PM                                    | 2:00 PM                                        | 3:00 PM                                    | 4:00 PM                                 | 5:00 PM                                     | 6PM                                                      | 7PM          |

|               | Regency East 1-3<br>(Ballroom Level) |                           | G-12 & G-11<br>1580 DPA<br>Revisions                               | Joint JC-13.2/G<br>Meeting   | i-12 Joint JC-1                                                                                      | 3.1/G-12 Meeting                          | $\setminus$                                                  | Joint JC-13.7/G-12<br>Devic                |                                                | Joint JC-13.5/G-12                         | Meeting (                               | G-12 & G-11 Spa                             | ce Subcommittee                                          | $\mathbf{D}$ |

| /ed 1/11      | Chula Vista (Lobby<br>Level)         |                           | JC-13.5 Meeting                                                    |                              |                                                                                                      |                                           |                                                              | JC-13.5 M                                  | eeting                                         | Chaired by NASA                            |                                         |                                             |                                                          |              |

|               | Pecan (Hill<br>Country Level)        |                           | Joint JC-13.1                                                      | /JC-13.4 Meeting             | G-12<br>Radiation RHA Subcommittee                                                                   |                                           |                                                              |                                            | G-12<br>A Subcommittee                         |                                            |                                         |                                             |                                                          |              |

|               | Live Oak (Hill<br>Country Level)     |                           | G-11 should<br>go to 1580 G-11 Committee Meeting                   |                              |                                                                                                      |                                           |                                                              | G-11 Commmittee Meeting                    |                                                |                                            |                                         | Reception - Lori's<br>CASH BAR - AL         |                                                          |              |

| Day           | Room                                 | 7:30 AM                   | 8:00 AM                                                            | 9:00 AM                      | 10:00 AM                                                                                             | 11:00 AM                                  | 12:00 PM                                                     | 1:00 PM                                    | 2:00 PM                                        | 3:00 PM                                    | 4:00 PM                                 | 5:00 PM                                     | 6PM                                                      | 7PM          |

| Thurs<br>1/12 | Regency East 1-3<br>(Ballroom Level) |                           | JC-13 Ge                                                           | neral Session                | ion Tech Talk: How<br>Does Automotive<br>Achieve and<br>Validate High<br>Quality and<br>Reliability? |                                           | *                                                            |                                            |                                                |                                            |                                         |                                             |                                                          |              |

|               | Chula Vista (Lobby<br>Level)         |                           | G-11 Committee Meeting                                             |                              |                                                                                                      |                                           | $\geq$                                                       |                                            |                                                |                                            |                                         |                                             |                                                          |              |

### NEPAG and JEDEC/G-11/G-12

#### • January 2017 Meeting

- Held NEPAG@JEDEC

- o Attended executive committee meetings

- Chaired Space subcommittee meeting

- Responsible for G-12 meeting notes (Roger)

- Co-lead task group on burn-in (Shri)

- Meetings with manufacturers

- Including State of the Art (SotA)

- Meetings with OEMs

- Provide Class Y status report

- ESD related Support (Shri)

- DLA Engineering Practice (EP) Study on electrostatic discharge (ESD)

- New JC-13 task group on ESD

- Active participation (Shri, Leif, Jennifer, John, Dale)

- JC-13.2 (monolithic microcircuits)

- ✤ JC-13.4 (radiation)

- ✤ G-11 (passives)

- ✤ G-12 (actives)

#### • Telecons

NEPAG

- Plastic encapsulated microcircuits (PEMs) for Space

- PEMs for Terrestrials/ Avionics

- JESD 625B and ESDA 20.20 Harmonization

#### Example of Updated Requirements, Microcircuits Burn-in (BI) (NASA Inputs 12 September 2016)

#### Status

- Task Group until recently was chaired by B. Rhoton. Taken over by N. Shindler going forward.

- Published Guideline document JEP163.

- DLA's Engineering Practice (EP) study on BI is complete.

- Task group is still open to address new concerns

#### • A New Concern

- BI of high-speed devices (frequencies approaching gigahertz range)

- What about hot spots on the die? For example, Serializer/Deserializer (SERDES) in a field-programmable gate array (FPGA) may run much hotter than the rest of the die.

- Practically no data on hot spots (no verification of models)

- Ambient vs. case vs. junction temperature

JEDEC PUBLICATION

Selection of Burn-In/Life Test Conditions and Critical Parameters for QML Microcircuits

**JEP163**

SEPTEMBER 2015

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

NEPAG

### Other JEDEC/G11/G12 Major Activities Supported by NASA

- Leak rate and residual gas analysis (RGA)

- New technology insertion (>2D packaging)

- GaN, SiC Working Groups

- Hybrid element evaluation

- Passives

- Radiation hardness

- Plastic encapsulated microcircuit (PEM) screening and qual flows

- Copper bond wires qualification, testing

### **NASA Electrostatic Discharge (ESD) Surveys of Manufacturers**

#### • Microcircuits:

- Candidate companies for NASA ESD survey are identified during the DLA audit.

- This is an independent survey by NASA--Not a part of the DLA audit process.

- The purpose of the survey is to better prepare smaller manufacturers with plans to develop space products.

- The findings of the survey are non-binding.

- There has been good feedback from companies that went through it.

#### **Electrostatic Discharge**

#### • NASA EEE Parts Bulletin (January – July 2016)

January–July, 2016 · Volume 8, Issue 1, Revision A, January 26, 2017 Special Edition on Electrostatic Discharge (ESD) (The NASA *EEE Parts Bulletin* has been published since 2009)

Note: This revision adds a number of details and corrects ambiguities in the original issue that was released August 31, 2016 (the K. LaBel article on partnering and the back-page material were not changed).

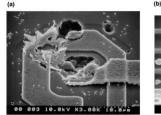

Damage from ESD is a major cost to the microcircuit industry in terms of time, money, and mission risk. We plan to release two issues. This first special issue deals with the need to upgrade specifications related to ESD and suggestions for better ESD practices wherever parts are manufactured, stored, or prepared for shipment. This issue also includes an article about partnering in radiation and reliability testing. The second special issue will describe examples of ESD-related problems. Figure 1 is an example of damage caused by ESD.

Figure 1. Examples of ESD damage to microcircuits (Images courtesy of JPL Analysis and Test Laboratory):

- A static random access memory (SRAM) device with 5-micron features was deliberately exposed to an 8000-volt pulse from a 100-picofarad capacitor. This produced an approximately 5.3-ampere peak current pulse lasting just under one microsecond. Metting of conductive traces is typical of such ESD damage and creates an open circuit path.

- b) An undefined microcircuit with 1-micron line widths that failed in service after being exposed to a pulse of approximately 500 volts. This caused a breakdown of the SIO layer and a short circuit in the part.

#### Upgrading ESD Control: Its Importance and Possible Strategies

A. What Is ESD and How Are ESD Controls Applied?

VEPAG

Electrostatic discharge or ESD in electronic parts is an electrical sparking event that functions like a tiny version of lightning. When two objects with different potentials are brought sufficiently close, a current flows toward the caused by friction of dissimilar materials (shoes on a carpet is a classic example), but even the difference in potential between a human body and an object may be enough to initiate an ESD event. For electronic parts, built to carry minute amounts of current invi livithinia bolts are a cause for concern If such

ground equalizing the potential. These differences can be

rent, tiny lightning bolts are a cause for concern. If such an errant current flow of an ESD goes along the outer case of a part or the outside of an ESD-resistant (antilatic) bag or shipper, there may be no problem. However, such a current goes through the part, serious damage hay result. ESD damage can include catastrophic damge and/or latent damage. Catastrophic damage is immelately detectable by the resulting loss of function and of in visible damage. Latent damage is not immediately detable because there is no loss of function and often no sible sign of damage. However, the part has been weaked and may fail in the field or (worse) in space.

his has always been a serious concern for electronic arts, but it has grown steadily more urgent.

he purpose of this article is to sensitize the entire space nomunity, and in particular, the standards-developingodies to the fact that the ESD requirements must be early specified in such standards documents so that verybody handling microcircuits, from manufacture to fial use can minimize ESD damage. Furthermore, the landards must be updated to reflect the present level of chnology.

b this context, the role of DLA (Defense Logistics gency) for the department of defense (DoD) becomes tal. The standardization branch of DLA develops and aninatins the military (MLI) standards, which are used for aninating high-reliability quality parts production for the 0.0 and for NASA. In addition, manufacturers and non-III, standards organizations provide inputs to the standrds.

hese standards are often enforced by periodic audits of arts manufacturers and their supply chains. The audit ranch of DLA officially conducts official enforcement. ASA actively supports DLA in both of these activities.

or the purposes of this article, we are focusing on monlithic microcircuits. The standard most commonly used y the U.S. space community for high-reliability microcirlists is MuL-PRF-38535, Integrated Cricuits (Microcirlist) Manufacturing, General Specification for: Any mirocircuit parts produced under the military system must in compliance with the requirements of this document.

he 38535 is the periodically changing overall document ontrolling microcircuit quality and reliability. The ESD asects of the document clearly need updating. For audiig, the requirements must be flowed down to the working udit, and it must be reflected in each manufacturer's uality management (QM) plan.

addition, the ESD-related standards used by other oranizations may provide ideas for upgrades to the MIL tandards. Conversely, it would be highly beneficial if the III. standard upgrades could be coordinated with those the other standards bodies so that practices throughout he industry might be as similar and interchangeable as ossible.

2

#### B. Why Improved ESD Control Practices Are Crucial

Microcircuit densification has increased pin counts significantly in the last decade, particularly for communication and computing products. NASA and the space community are using 1752-pin counts, and higher counts are growing more common in the general market.

Current ESD rating methods were developed with typical pin counts in the twentiles. Applying these old device testing standards to modern high-pin count products can cause severe problems. Testing times increase dramatically. Worse, wear caused by repeatedly stressing the same path and the increasing influence of tester parsalic losses (parasitics) can lead to false-positive failures.

The increased capabilities attained by increasing parts density has come at the cost of greater sensitivity to ESD. Thus, it becomes increasingly important to implement better methods of controlling potential damage from ESD. A wide assortment of books and journal papers provides information on methods for mitigating ESD.

For high-reliability microcircuits (where a part may cost as much as tens of thousands of dollars), organizations often develop and enforce required policies and procedures designed to mitigate ESD. These policies and procedures are codified in standards.

Furthermore, the landscape of microcircuit part production, handling, and shipping has changed radically. Because of the increased complexity of parts, the paradigm of a manufacturer shipping directly to a customer has largely given way to a highly dispersed production environment, which in turn, often requires highly dispersed ESD control among a number of organizations. Table 1 shows all the steps at which production or use of a microcircuit might be done by shipping to another facility. (The most extreme cases of maximum dispersion are more likely with new products such as flip chips.) Moreover, each of the steps involves at least one environment each for working on the part, storing the part, and shipping the part to the next step in the production.

Much as increased pin counts increase the susceptibility to ESD, increasing the number of shipping steps in the supply chain increases the number of points where ESD damage may occur.

lures

DEC

other

ht in-

3

It is important to recognize and fully address all the risk points to which ESD sensitive parts are subjected: from when they are fabricated and delivered from the original component manufacture's (OCM) site; through supply chain avenues to user inventions; then on to kitting and upper-level printed circuit board (PCB) level assembly, test and verification; and evenually to final box level assembly, test and final system level test. This is particularly important for handling, packaging, and shipping of ESD Class 0A devices (<125 volts in the Human Body Model).

> Are all three commonly used ESD models still valid or should the standards focus on one or two

models?: Those models are 1) human body model (HBM) based on people accumulating electric charges; 2) charged device model (CDM) based on materials becoming charged after they rub against other materials, and 3) machine model (MM) (designed to simulate a machine discharging through a device to ground).

- Do we want a standard for reducing the number of pin combinations required for testing?

- Would statistical pin testing be a good approach?

- How can the testing time be reduced without losing useful information (and significantly impacting the test data)?

- Should the MIL standards be expanded to include charged device model (CDM) testing?

- How do the new 2.5D and 3D configurations affect ESD testing?

We need to consider future trends when revising test standards. This issue is growing more important because the unit cost of contemporary devices are very high (and are growing costiler as more functionality is added), on the order of several tens of thousands of dollars per unit. Poor ESD environment for such products creates possibility of damage/ latent damage to them, both of which could be very expensive. Costs for implementing an ESD-prevention program are miniscule compared to the overall cost incurred in dealing with ESD damage.

The above concerns were presented by NASA representative Michael Sampson at the June 2016 G12 Space Subcommittee meeting. He proposed that the military documents that control the ESD requirements for testing and rating ESD event severity be reviewed and updated as a first step. As part of this update process, he suggested that Defense Land and Maritime (DLA), which serves as the qualifying authority to maintain the MIL system of parts qualification, perform an engineering practice (EP) study on ESD to detail these issues and compare possible specification changes with those being implemented or proposed by other organizations, in particular the NASA Inter-Agency Working Group related to ESD (NASA IAWG-ESD). Ideally, coordination among the various standards-setting organizations would result in updated ESD standards with a great deal of commonality DLA shared the results of their EP study at the JEDEC meeting held in January 2017. Based on the EP study and responses to it, JEDEC (JC-13) has opened a task group to resolve issues related to ESD.

These document changes will require review and coordination with associated reference documents from other organizations to bring consistency.

## **Issues from Microcircuit / Other Audits and Methods of Resolution**

| Audits                 |                                                                       |         |                                                              |                                              |                                                |                                        |

|------------------------|-----------------------------------------------------------------------|---------|--------------------------------------------------------------|----------------------------------------------|------------------------------------------------|----------------------------------------|

| Class Y                | New Technology I                                                      | nfusion | NASA Parts<br>Bulletin                                       | DLA<br>Engineering<br>Practice (EP)<br>study | G-12<br>Task Group<br>(TG)                     | MIL-PRF-<br>38535<br>Revision K        |

| Burn-in                | Varied interpretat<br>requirement                                     |         | DLA<br>Engineering<br>Practice (EP)<br>study                 | JEDEC<br>Task Group<br>(TG)                  | JEP163.<br>TG still<br>open                    |                                        |

| Underfill              | Difficulties in me<br>requirement                                     | •       | NASA Parts<br>Bulletin –<br>Special Edition<br>on Underfills | DLA<br>Engineering<br>Practice (EP)<br>study | JEDEC Task<br>Group                            | Resolved                               |

| ESD                    | Old/inconsistent<br>requirements<br>(e.g. 3 zaps vs<br>1 zap per pin) |         | NASA Parts<br>Bulletin –<br>Special ESD<br>Edition           | DLA<br>Engineering<br>Practice (EP)<br>study | DLA presented<br>EP results in<br>January 2017 | A JEDEC<br>ESD task<br>group<br>formed |

| Crystal<br>Oscillators | Per manufacturers<br>sales for QPLS                                   |         | NASA Parts<br>Bulletin – in<br>preparation                   | DLA EP study<br>planned                      | DLA talk at<br>Space meeting<br>last September | New issue                              |

NEPAG

Process Flow:

ما:لم

\*DLA Audits: Major issues uncovered during DLA audits

\*NASA Parts Bulletin – Special Edition: Gives subject matter background. Provides results of NASA evaluations, ESD surveys, etc.

\*DLA EP Study: A large survey of manufacturers, users, others.

\*JEDEC/G11/G12 Meetings: Where discussions are held.

### Microcircuits Moving with the Times

#### • NASA Class Y experience:

NEPAG

- NASA-led new technology infusion

- A new way to conduct business

- Supplier offered a product of system-on-a-chip (SOC) complexity,

- Xilinx Virtex-4 and -5 FPGAs (ceramic-based flip-chip non-hermetic construction)

- Of great interest to hardware designers

- It represented advances in packaging, smaller feature sizes

- □ Flip-chip, CGA. 65nm–90nm feature sizes.

- But, it didn't fit any of the existing categories

- □ So, a new Class Y was introduced

- ✤ It also made us realize that we had reached an unchartered area

- Somewhere near the boundary of parts and boards

- Suppliers and space community had considerable discussion on developing requirements for Class Y (some of which would also apply to Class V).

- ✤ Examples of new requirements put in 38535K:

- Post column attach electricals (screening)

- Package integrity demonstration test plan (PIDTP) quality conformance inspection (QCI)

- ✤ The concept of doing screening and qualification testing remained intact

16

### Infusion of New Technology into MIL/Space Standards PIDTP and Its Applicability

#### • Issue

How to address the manufacturability, test, quality, and reliability issues unique to new non-traditional assembly/package technologies intended for space applications

#### • Solution Proposed

- Introduced a new concept called package integrity demonstration test plan (PIDTP)

- Each manufacturer shall develop a PIDTP that shall be approved by the qualifying activity after consultation with the space community. Ref: MIL-PRF-38535K, Para B.3.11.

#### • The PIDTP requirement would apply to:

- Non-hermetic packages (e.g., Class Y). Ref: 38535K, H.3.4.4.1.1.

- Flip-chip assembly. Ref: 38535K, H.3.4.4.1.2.

- Solder terminations. Ref: 38535K, H.3.4.4.1.3.

- Microcircuits employing more than one of above technologies shall include elements for each in the PIDTP.

Ref: 38535K, H.3.4.4.1.

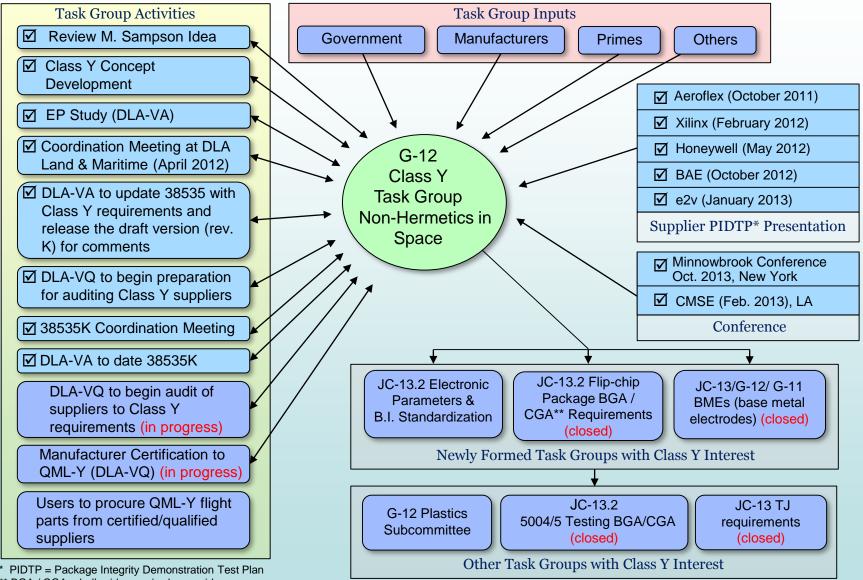

### Infusion of the New Class (Y) Technology into the QML **System for Space**

NEPAG

\*\* BGA / CGA = ball-grid array / column-grid array

### **Class Y Qualification / Certification Status**

#### Qualified Manufacturers

• Honeywell, Plymouth, MN.

#### Certified Column attach service providers

- o Six Sigma, Milpitas, CA

- Micross, Crewe, UK

- o BAE Systems, Manassas, VA

- Honeywell, Plymouth, MN

#### Certified Manufacturers

o Cobham, Colorado Springs, CO

#### Certification Planned

NEPAG

- Xilinx, San Jose, CA

- Still no specs for BME (Base Metal Electrode) IDCs (Inter-Digitized Capacitors)

- o e2V, Grenoble, France

- Cypress, San Jose, CA

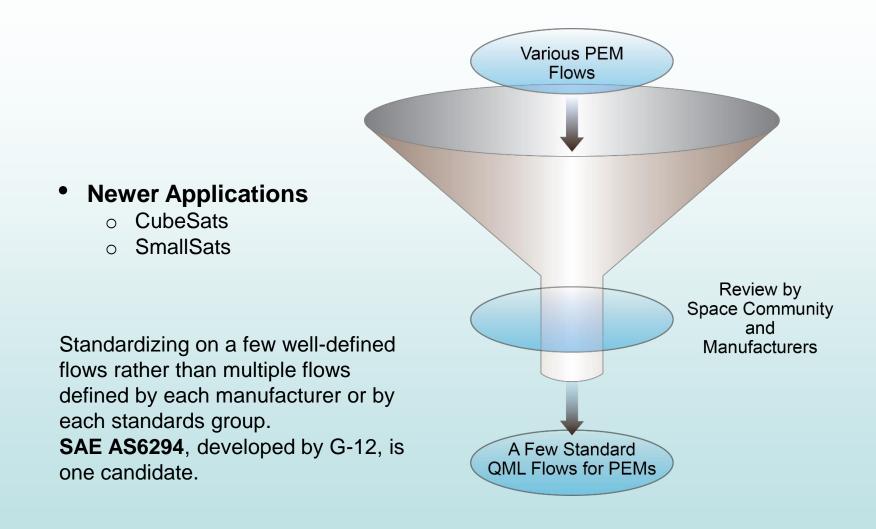

### **PEMS for Space**

#### Working toward Standardized Flows for NASA CubeSats and SmallSats

- There are many new NASA flight missions categorized as CubeSats and SmallSats. During the weekly NEPAG telecons, the group has discussed what kind of standard products would fit those applications, including commercial-offthe-shelf (COTS) plastic encapsulated microcircuits (PEMs). NASA is supporting SAE SSTCG12 committee activities with the goal of developing PEM standard flows for avionics, and space applications.

- At least three parts manufacturers have recognized the need for this newly developing market and are offering customized parts. Cobham Aeroflex has several flows assigned based on extent of testing to assist users in picking the best parts. Similarly, Texas Instruments offers parts in five different versions, including their QML offerings. Linear Technology plans to offer PEM products with guaranteed total dose radiation (rad tolerant, RT) ratings. Also, there is an existing QML N flow for standard non-space PEM devices.

- These are all good developments. However, it would be cumbersome to manage multiple nonstandard flows. Moreover, some of these approaches may or may not apply to NASA missions depending on acceptable risk levels. The ideal situation would be for the space community and manufacturers to agree on a limited number of standard QML PEM flows to offer solutions for small missions (CubeSats, NanoSats, SmallSats, etc.). In addition, there are DLA's Vendor Item Drawing (VID) program and parts built for automotive applications.

- All this needs to be discussed.

### **PEMs for Space**

### **DLA's VID (Vendor Item Drawing) Program**

#### Current Supplier's Program Benefits

- 1. Single Standardization Document

- 2. Controlled baseline.

- 3. Enhanced product change notification of processes, materials, electrical performance, finish, molding compounds and manufacturing locations.

- 4. Extended temperature performance.

- 5. Enhanced Pedigree Reliability and electromigration checks, electrical characterization over temperature and confirmation of package performance over temperature.

- 6. Enhanced Obsolescence management.

- 7. No pure tin.

- 8. No copper wire bonds.

See the attached listing or check our website for an up to date list of product coverage.

#### DSCC ANNOUNCES THE RELEASE OF A NEW TYPE OF STANDARDIZATION DOCUMENT.

DSCC is releasing new Vendor Item Drawings (VIDs) almost daily. These documents have been created to provide a procurement vehicle for en-

hanced commercial products. Specifically, commercially available microcircuit products are being documented for the first time on a standardization document. Use of these DSCC VIDs will avoid the use of manufacturer generated specification control drawings (SCDs) or manufacturer's VIDs and avoid the potential proliferation of non-standard products. The participating manufacturers have agreed to provide information and services that have not traditionally been associated with commercial products. See our website for a list of documents that are currently available.

All Vendor Item Drawings are <u>NOW</u> available on the DSCC web site

http://www.dscc.dla.mil/Programs/MilSpec/

• Analog and digital functions offered.

### **Evaluation of Automotive Microcircuits**

#### • Existing automotive parts market

- Plastic packages

- No screening is done

- Much testing is done at the wafer level

- Limited qualification

- The customer must enforce any desired requirements

- Manufacturers self certify no DLA-type regulators

- The system works because of high-volume production That is the customer's power to enforce upgrades

#### • Evaluation is in progress at Navy Crane

- Screening and qualification are planned

- Tight budget

- ✤ Qualification will be limited to life test

### **Current Status of Hermetic and Non-Hermetic QML Space ICs**

#### • Classes V and Y

- The demand for standard hermetic space products (Class V) continues to stay strong. We review 18–20 new SMD drawings every year, many of which include guarantee for radiation hardness. It shows that despite a push towards COTS to address CubeSats, SmallSats, and other applications, the standard space parts are still pretty much in demand.

- Development of a new QML Class (such as the Class Y we did for ceramic based non-hermetic microcircuits) takes a fair amount of work.

- The screening and QCI requirements for Class V and Y are similar except for Class V is hermetic, Class Y is not.

- In the process of developing requirements for Class Y for Xilinx Virtex FPGAs and other products of similar complexity, system-on-a-chip (SoC) with a large number of columns (1752 for Xilinx), it was realized that we had reached an unchartered area: somewhere near the boundary of parts and subassemblies. Many compromises had to be made, such as room temperature (rather than over temperature) electrical testing post column attach.

#### Hermetic and Non-Hermetic QML Space ICs in Near Future

#### Concluding Remarks

- The extent of support to flight projects/programs/experiments provided by parts engineers working at NASA would broaden: it would cover a much wider spectrum of parts, from COTS and automotive to traditional standard products.

- The next generation of parts, 2.5D and 3D, will require considerable work in developing standards.

- The boundary between monolithic and hybrid microcircuits is going to keep getting fuzzier. At some point we would wonder if it wouldn't make sense to have one performance specification for all microcircuits, including those in 2.5D/3D configurations (combine MIL-PRF-38535 and MIL-PRF-38534)?

- Higher chip speeds and increasing chip densities will require a shift in the paradigm for electrical testing and burn-in.

### **NASA Workshop**

#### • Workshop

- NASA Electronic Technology Workshop (ETW) combined with Small Missions Workshop is held in June every year

- ✤ The next ETW will be June 26-29, 2017

- Venue: Goddard Space Flight Center, Greenbelt, MD

- Past papers posted on NEPP Website: nepp.nasa.gov

- See above website for other details

# http://nepp.nasa.gov

#### ACKNOWLEDGMENTS

The research described in this publication was carried out, in part, at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration. Help is gratefully acknowledged from Mohammad Mojarradi, Jeremy Bonnell, Roger Carlson, Joon Park, and Michael Sampson.

Copyright 2017 California Institute of Technology. Government sponsorship acknowledged.

#### DISCLAIMER

Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not constitute or imply its endorsement by the united States Government or the Jet Propulsion Laboratory, California Institute of Technology.