Package and Die Attach Comparisons for High Power GaN Devices

StratEdge Corporation Casey Krawiec and Erik Sanchez

STRATEDGE

9424

# **Company Snapshot**

- StratEdge founded in 1992

- Focus on compound semiconductors

- Packages and assembly services for RF, microwave, and millimeter wave devices

- Headquarters and manufacturing facility in San Diego

- Private corporation

- ISO 9001-2015 certified facility

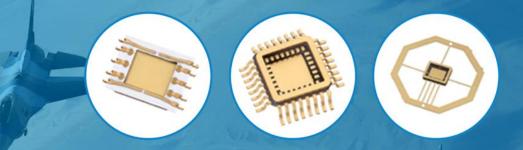

### StratEdge Package Technology

High Frequency High Speed High Power

### Materials:

- Packages made from hardened ceramic substrates

- Post-fired metallization of ceramic with thick film pastes

- Alumina, Beryllium Oxide ceramics laser machined

- Molded ceramic packages

- Crack resistant alumina-filled glass

- Fe-Ni-Co leads, bases, and rings for hermetic sealing

- Addition of high thermal conductivity base materials

- CuW, CuMo, CMC laminate

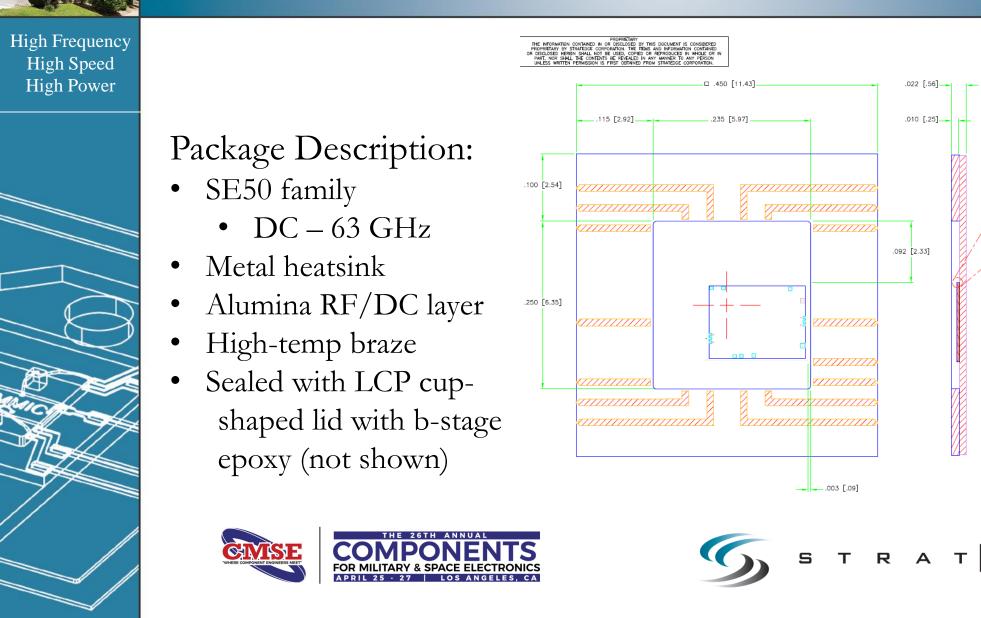

### **Thermal Analysis**

High Frequency High Speed High Power

> Objective: Conduct a series of thermal simulations to compare how well heat is dissipated from a Gallium Nitride device while varying the die attach material and package heat spreader (base) material.

## Package and Chip Assembly

E

D

G

Ε

# Base Requirements for High-power Device

### High Thermal Conductivity

• Gallium Nitride (GaN) chips operating at high frequencies with high power generate heat that needs to be dissipated

Compatible Coefficient of Thermal Expansion (CTE)

• As the package heats up during operation, the base needs to expand close to the same rate as the GaN chip to prevent physical damage

### Package Bases Studied

High Frequency High Speed High Power

#### CMC laminate

- Molybdenum layer between copper

- Cu:Mo:Cu 1:3:1 Thickness Ratio

CuW (85/15)

- Copper tungsten composite

- 15% Copper / 85% Tungsten

| CMC Base, Thermal Conductivity<br>Layer Thickness (inches) | CuW Base, Thermal Conductivity,<br>Layer Thickness (inches) |  |  |

|------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Copper (401 W/m K), 0.002                                  |                                                             |  |  |

| Mo (139 W/m K), 0.006                                      | CuW (190 W/m K), 0.010                                      |  |  |

| Copper (401 W/m K), 0.002                                  |                                                             |  |  |

• Silver-filled epoxy system

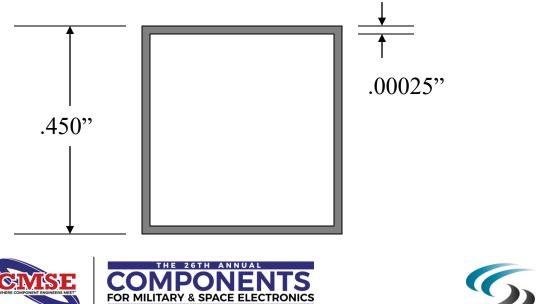

### AuSn Eutectic Solder

• 80% gold 20% tin

|                              | EPO-TEK®<br>H20E | AuSn    |

|------------------------------|------------------|---------|

| Bond Line Thickness (inches) | 0.0015           | 0.00025 |

| Thermal Conductivity (W/m K) | 2.5              | 57      |

**Die Attach Material**

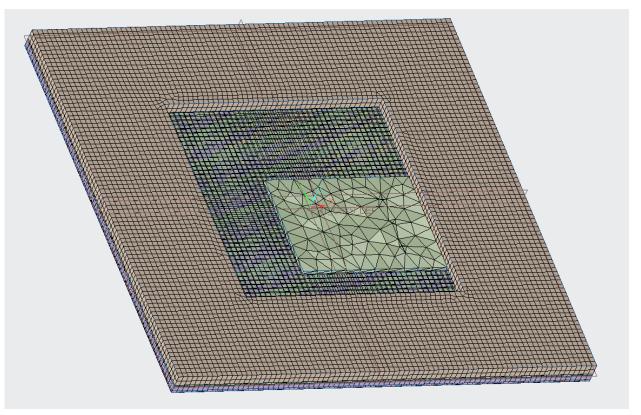

### Simulation Software: PTC Creo Ansys

- High Frequency High Speed High Power

- Creo Ansys Simulation is a finite element tool we used to evaluate thermal performance of a microelectronic system.

- Creo Ansys is a partnership between PCT and Ansys.

CIVISE

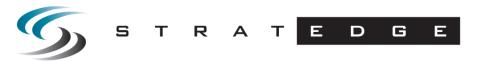

# Steady State Thermal Analysis of a GaN Device

GaN device, 0.150" long x 0.113" wide

- 10 Watts dispersed over the area of three output stages

- Each output stage generates 3.333 W

- Each output stage broken up into eight heat sources

- Heat generated is applied at the top surface of the GaN-on-Silicon Carbide (SiC) device

### Boundary condition

• The bottom edges of the package are set at a constant temperature

### Steady State Thermal Analysis of a GaN Device

- Boundary condition: Area between 0.4495" x 0.4495" and 0.45" x 0.45" (base outer dimensions)

- Perimeter is set at 75°C

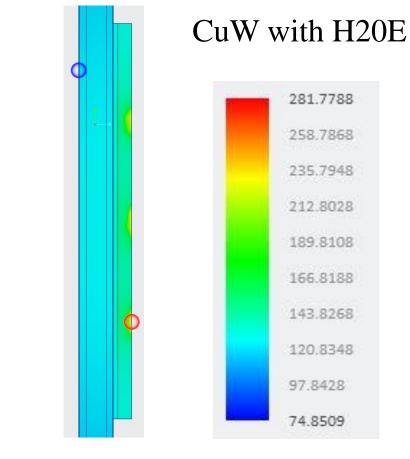

## Visual Comparison of Temperature Gradients

High Frequency High Speed High Power

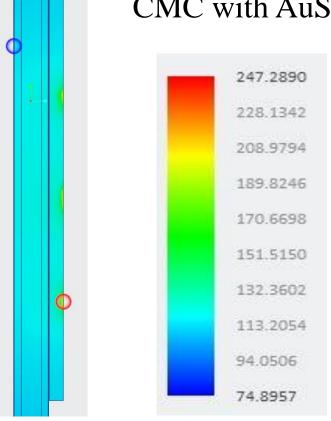

#### CMC with AuSn

### Heat Sources on Die

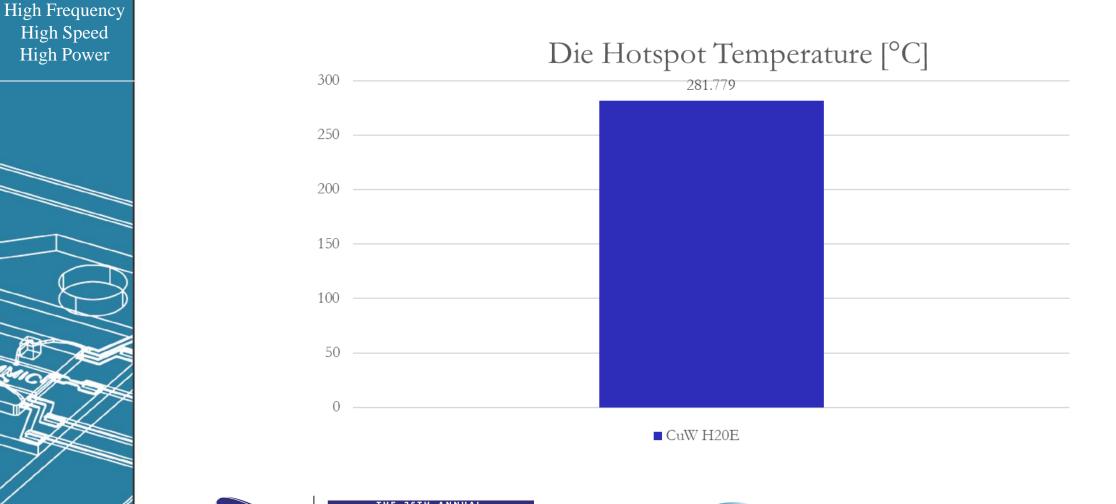

### Results: H20E on CuW Base

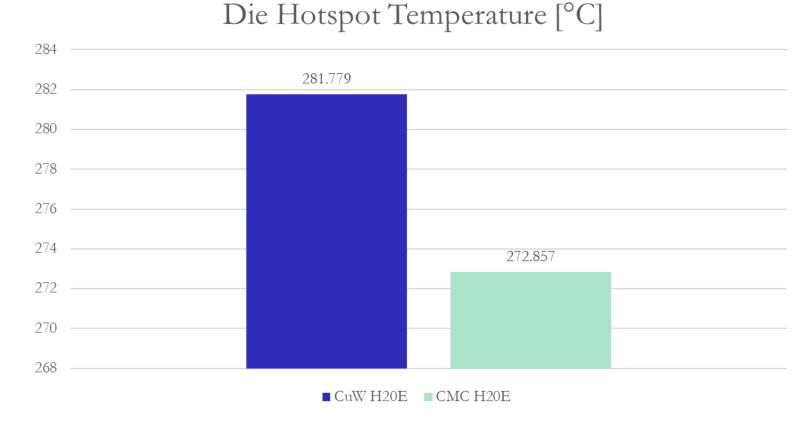

### Results: H20E on CuW and CMC

High Frequency High Speed High Power

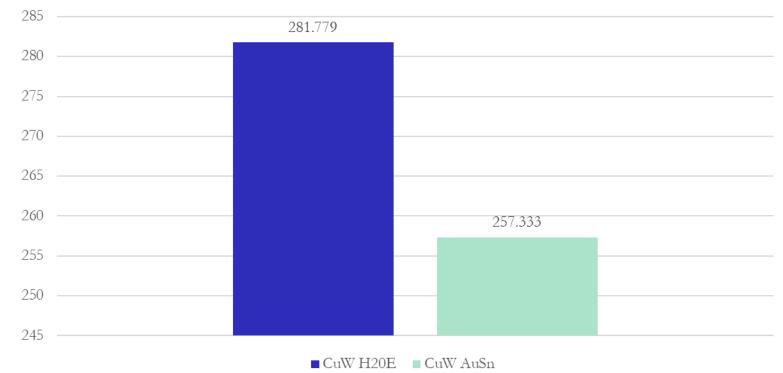

### Results: H20E and AuSn on CuW

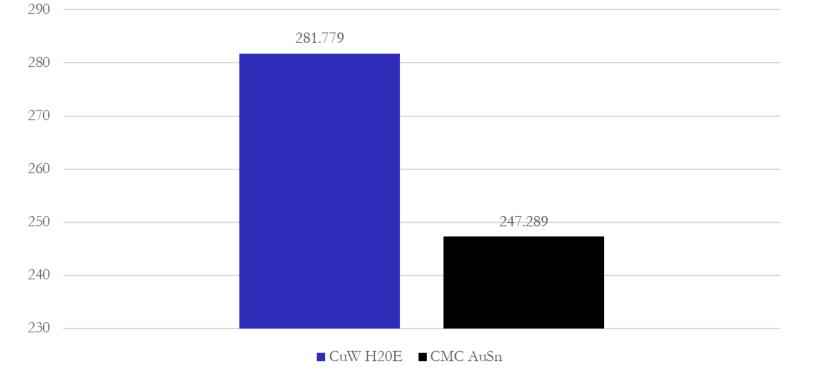

### Results: H20E on CuW vs. AuSn on CMC

#### Die Hotspot Temperature [°C]

| Sı | Imn | nary |

|----|-----|------|

|    |     | -    |

|          | H20E Epoxy | AuSn Solder |

|----------|------------|-------------|

| CuW base | 281.8      | 257.3       |

| CMC Base | 272.9      | 247.3       |

Transistor temperatures for different combinations of base material and die attach material (all temperatures in degrees Celsius)

- CMC base ~10 °C cooler than CuW Base

- Eutectic (AuSn) die attach ~25 °C cooler than EPO-TEK® H20E

- Comparing CMC with AuSn to CuW with H20E: Total temperature delta is 34.49 °C

- Validated empirical results previously provided by customers

- Provides StratEdge a foundation for future studies

Please contact me at <u>c.krawiec@stratedge.com</u> if you have any additional questions.